tessent dft run 过程中会报告DFT_C6 和 DFT_C9 的error 类似

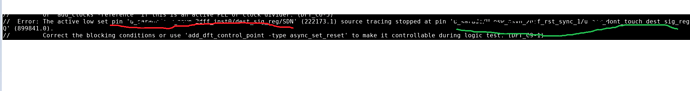

DFT_C6

意思是说你的FF/CK 是一个定值,不可控。

这种情况可能是designer 电路在这个项目中不用,但是又不想删除所以保留下来。对于dft来说有两种解法

method1: bypass 一条testclock 接到上面来让它可控。(这个其实能提高coverage但是这个不用的ff个人感觉dft测不测都无所谓)

method2: 直接用add_nonscan_instance 来让它不上chain

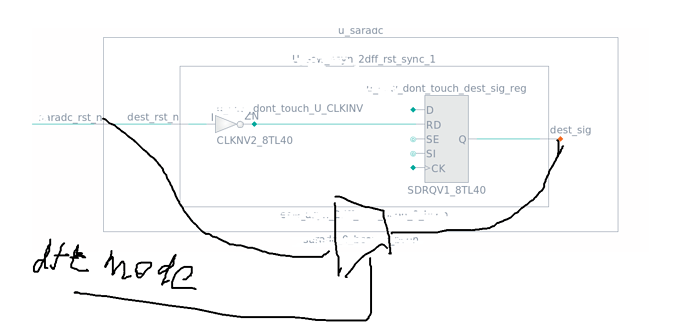

DFT_C9

类似这样

意思是复位或者ck端往前trace时候发现是由 ff/q 驱动的,这样不可控。

解法,给它bypass一下,跟DFT_C6 method1 一样。

如何bypass

open_visulizer 打开tessent gui (貌似只能setup, analysis 打开,insert好像不行)

然后打开search

把绿色这个驱动的instance贴到search里面然后schematic 显示

然后点pin trace driver trace load 。找到hier pin。

然后下一步就是用命令做一个我黑色线画的事情用mux做一个bypass

用intercept_connect 来做。 然后select就是你的dft enable信号如果select 1 走 input2 这一路这样就bypass了

补充,

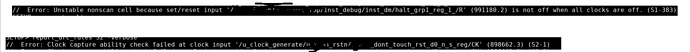

C6 drc 描述的是ff的CK 不可控。

C9 描述的是ff的reset端不可控。

对于C6这种CK不可控的情况在用intercept_connect 的时候一定要用-leaf_instance_prefix 来指定你创建mux的instance 前缀

![]()

因为这些CK 可控后,需要在前面垫occ 来在ATPG 的情况下能够进行 clock select 和 clock chopping 。

来进行shift capture .

垫occ的时候会在occ specify 里面写入

让occ在前面有occ_node的instance mux/Z 后面垫occ

有的时候C6 时候不需要垫occ因为有时候你bypass的那个clock network 前面就有occ 所以不需要垫。这个得具体问题具体分析

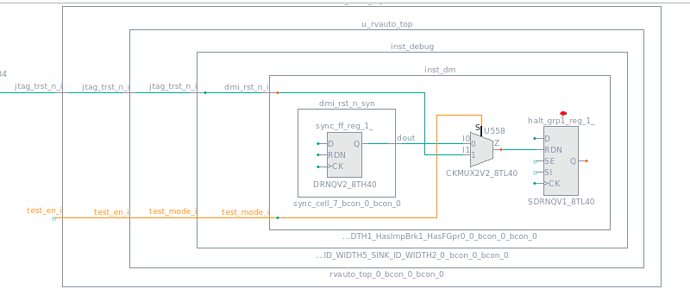

关于S rule . S rule 得处于set_context dft -scan 用 check_design_rule 可以报告出来。

类似

open_visualizer

可以看到sel 没有接用命令接上就解了

关于S2 可能是你的ff是用来分频的div ff 所以本来就不用上chain。所以用add_nonscan -instance 应该就能解掉。