PR 完毕后需要run lvs 保证layout verilog 一致

首先需要把verilog 转换成spice model

需要指定cdl文件

有一些ULVT cell 或者iso cell 有bias pin VNW VPW

记得写一个cdl 告诉calibredrv 这些bias pin 连接否则 instance 会incorrect

(这些VNW VPW 不会在verilog 里面连接, 但是抽spice model 时候可能需要连接关系,防止spice model 有问题)

然后开始转换cmd

转换完毕后会得到design 的spice 文件

然后开始LVS

CMD

hcell.lis

hcell.list cell map 关系

可以用这个抓出所有的cell

在比对cell的时候按照我指定的cell 层级来比对。

方便LVS 出错时候debug , 如果不加,有时候出错报告的cell 名字奇奇怪怪的。

加了后会报告出错cell名字方便debug

后面跟的文件是工艺厂商提供的。

里面需要指定 design gds 和 design spi 文件类似

然后跑吧,

跑完了

看lvs.rep

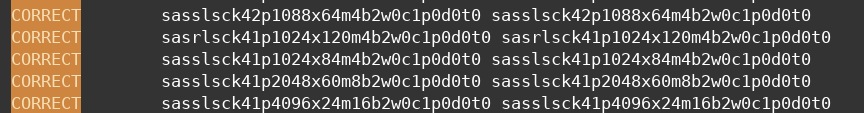

过的cell显示

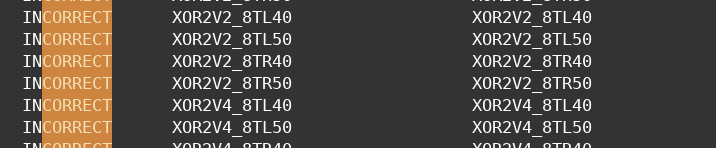

没过的显示

如果lvs 不过,可能是你的.v 逻辑连接和layout 不一致

根据log 中提供的信息

启动invs 去看吧。 比如 invs 里面marco 右键 select net

这种应该route的没有route的就很可能导致lvs fail

另外在calibre 里面start RVE load LVS db 可以详细看有哪些lvs viols. 对照着invs 看

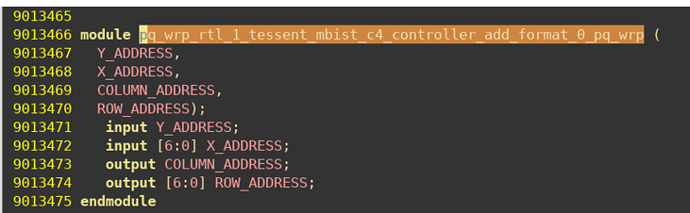

我来share一个我遇到的问题吧。 syn netlist有一个module 里面全是buffer ,pr 后就只剩下 空module了

类似

然后我run lvs 报告我的instance 不match source 有的 layout没有解的方法也简单

在LVS 脚本加入

LVS SPICE CULL PRIMITIVE SUBCIRCUITS YES

主义LVS脚本注释用//

或者

LVS Filter module_name OPEN SOURCE

在LVS 脚本include 这个

就不会比对空module

此时感觉LVS 的笑脸格外亲切 虽然我常吐槽这个笑脸看起来很诡异