在使用PCIe IP的时候,ACS功能是必须要验证的一个功能,他的功能根据IP的databook和网上的资料总结如下:

- 什么是ACS功能,Access control services,其主要是对于作为SW使用的PCIe接收到的TLP进行进一步处理,这些处理可能包括,通过检查BDF值与SW自己的BDF范围是否对应,选择是否丢弃该TLP包,并且产生对应的ACS interrupt。等等一类行为;

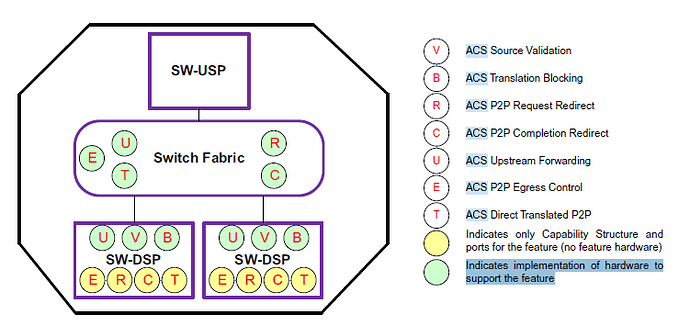

- 作为SW使用的PCIe IP可能包括的功能如下:

从上图中可以看到,绿色的功能点是硬件上可以实现。并且需要测试的。

3.各个功能点的说明:

V:source validation TLP来源正确性,验证一个pcie设备能否有权访问另一个pcie设备

B:阻止设备进行地址转换,实现设备之间的内存访问隔离,启用该功能后,启用该功能后,pcie设备只能访问自己的内存空间,不能范文别人的。

R:在PCIe拓扑结构中,两个端点设备可以通过Switch进行直接对等通信,这种通信方式称为 Peer-to-Peer。启用Peer-to-Peer request redirect后,对等请求可以被重新定向到Root Complex,然后再转发到目的端点。

C:P2P completion redirect 是PCIe规范中定义的一种机制,用于重定向对等设备(Peer-to-Peer)之间的完成(Completion)数据传输。

其原理是:

- 当设备A向设备B发出memory read/write请求时,该请求需要设备B产生一个完成(Completion)数据包发送给设备A。

- 若不使用P2P completion redirect,完成包会直接从设备B发送到设备A。

- 启用该机制后,完成包会先发送到Root Complex,然后再由Root Complex转发给设备A。

P2P completion redirect的主要作用是: - 允许Root Complex检查和修改对等设备间传输的数据。

- 避免对等设备之间形成无监管的直接通信通道。

- 阻止设备直接读取另一设备的保密数据。

- 提高对PCIe通信的安全监控和管理。

- 但是付出的代价是完成数据传输的延迟会有少许增加。

所以该机制通常用于提高多孔PCIe环境下的安全性,但会损失一些性能。

U:ACS Upstream Forwarding 的作用是

允许端点设备(Endpoint)通过上游端口(Upstream Port)来访问系统内存。

通常情况下,端点设备只能访问在总线号、设备号和函数号寻址空间内分配给它自身的资源。

但有些场景下,需要让端点设备能访问系统内存或其他端点的内存区域。

此时就可以使用 ACS Upstream Forwarding 来实现: - 端点设备发出的访问系统内存的请求,会转发到RC(Root Complex)。

- RC根据预置的访问控制规则来决定是否允许此请求。

- 如果请求被允许,RC就会将请求转发到系统内存。

- 然后将内存读取的数据返回给发起请求的端点设备。

ACS Upstream Forwarding 需要硬件和软件都支持,才能正确实现端点对系统内存的访问控制。

它提供了一种相对安全、可配置的机制,来选择性地开启端点设备对系统内存的访问权限。

E:ACS P2P Egress Control的作用

控制一个端点设备向对等端点设备发送请求的能力。

当ACS P2P Egress Control被启用时: - 一个端点设备(EP)只能向RC(Root Complex)发送请求和完成(Completion)包。

- 它不能直接向对等EP发送读写内存空间的请求包。

- 所有EP间的交互必须通过RC进行转发。

启用该功能的目的是为了加强对端点设备(EP)的出口(Egress)方向通信的访问控制。

它可以防止端点设备直接读写其它端点的内存空间,避免未经授权的对等访问,提高系统安全性。

但这也会降低端点间通信的效率。因此需要根据使用场景进行权衡。

总体来说,ACS P2P Egress Control为PCIe基础设施提供了更好的隔离与安全控制能力,适用于要求安全性更高的场景.

4.测试举例

我们以ACS source validation举例测试,首先梳理一下source validation的具体功能过程:

“当ACS Source Validation Control Bit被使能时,Downstream Port将会检查该Port接收到来自下游设备发上来的Upstream Request的bus number来确定该Upstream Request是否真正来自Switch Downstream Port的下游dev发出的。如果接收到的Upstream Request的Requester ID中的bus number不在Switch Downstream Port的Secondary Bus Number Register和Subordinate Bus Number Register的范围内,则该Switch Downstream Port将会产生一笔ACS Violation Error。”

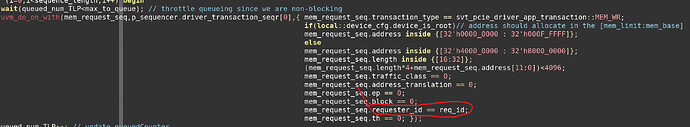

所以我们需要开启source validation control,然后VIP发送一个bdf号,主要是bus num号和dut的bus num不一样的TLP包,就会触发该违例,进而产生一个acs violation error。

同时在VIP的seq中将TLP包的rquestert_id值(requester_id就是TLP Header中的BDF值)修改为错误的bus num。

这样就会发出含有错误的BDF号的TLP包,同时DUT接收到该TLP包后会产生对应的中断。

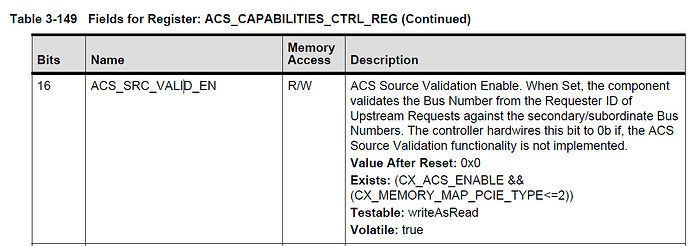

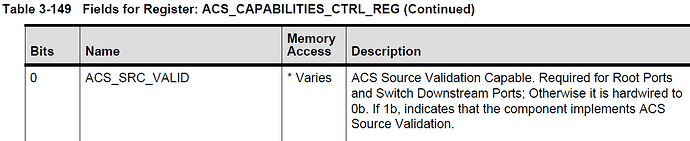

- 额外需要注意的一点,在配置PCIe打开ACS src violation功能时,对于寄存器的配置有一点要求。

在测试ACS功能时候,需要将ACS_CAPABILITIES_CTRL_REG寄存器的cap位和valid_en位都拉高。

但是如果直接配置32’h00010001此时16bit的ACS_SRC_VALID_EN是配置不进去的:

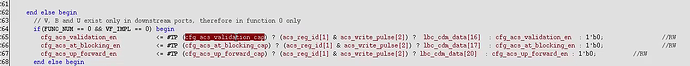

此时ni你看到的波形如下,发现validation_en没有生效。

这是因为:

在代码中,acs_validation_en是需要在cfg_acs_validation_cap=1的情况下才能完成的。所以需要先配置0bit为1,之后在配置16bit为1才可以完成配置;