从我开始进入行业实习开始,就会听说PR 摆floorplan 需要数据流等信息。需要知道模块交互。这在我心中扎下了深根。

但是随着工作年限和经验的增长,以及实际项目的历练。我对这个问题理解变得深入。事实上CHIP 顶层floorplan不是一个简单的活,也不是简单的某一个人或者某一个团队就能定下来的(当然小型soc和testchip除外)它需要各个部门乃至市场部门的通力合作相互拉扯来得到的结果)下面我就简单谈谈。

市场部门: 调研市场,与客户探讨需求。搜集竞争对手产品的PPA 参数。 与架构部门合作。要什么架构,买谁的IP , 我们的chip要支持哪些功能。 最终的目的都是大致确认下来CHIP 的大小。 和出PAD 样式, 以及可行性。( 这个很重要。因为需要知道客户PCB 的使用情况,甚至你可以通过PCB 和封装信息来推导出来竞争对手的chip floorplan 大致可能是什么样子)。当然成本也在考量内。

架构封装部门: 根据市场的需求,给出PAD 的位置和可行性。 我接触的wirebond 封装比较多。比如你的面积大小是固定的情况下。PAD 过多就摆不下,需要考虑PAD 复用这个牵扯到功能。 比如某一边的一部分上由于种种原因PAD 需要SIP 系统封装。而剩下的一部分为了节省面积需要塞满PAD 这样引线出来就需要封装斜着打线,需要封装部门看看可行性。

DFT 部门: 需要和架构设计商量你TDI TDO TCK TMS TRST RESET_N REF_CLOCK DFT case value PAD 这些都使用哪些PAD 可不可以复用。 哪些PAD 你必须要用。通常都是能少尽量少在可能的前提下。

PR SYN 部门: 需要在上面的信息情况下,将问题更具体化。在架构确定PAD 的情况下。你需要加入power pad 有些模拟单元使用的power pad 是不和数字共用的。有的模拟单元使用的power pad 是独立的。有的模拟和数字单元power pad 之间需要隔开。 特殊IP 的pad拜访要根据spec 说明来。 当某一个边过长时候你可能需要多组power pad 来保持IR 。 同时你需要工作模式的信息。比如某2个完全一样的PLL 不会同时工作。是不是有可能它们可以share power pad

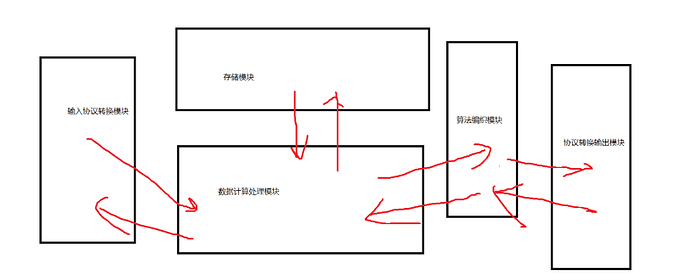

顶层的floorplan 需要考虑block数据流向。很有趣的是通常CHIP顶层都无非分这些模块。(至少我见到的是这样)

就是你总能找到这些模块的踪迹。

输入输入协议模块,各种协议从chip外获取信息。PCIE I2C SPI QSPI I2S HDMI …

存储模块, 存储数据的模块DDR SRAM FLASH

数据计算模块 (控制模块也划分在内 , 对信息处理计算)

算法编制模块 ( 对数据根据独有的算法进行处理)

你一般都会从架构哪里得到这样的消息。这样你的FLOOR PLAN 肯定是会有一个数据流向

举个很简单的例子

比如你的数据输入和输出在chip上下两侧。

你肯定不能按我图中这样来floorplan

这样就会按照绿色线detour.

行先聊这么多。也是我有感而发。